# CS 31: Intro to Systems Digital Logic

**Kevin Webb**

Swarthmore College

September 13, 2022

# Reading Quiz

# Today

- Hardware basics

- Machine memory models

- Digital signals

- Logic gates

Circuits: Borrow some paper if you need to!

- Manipulating/Representing values in hardware

- Adders

- Storage & memory (latches)

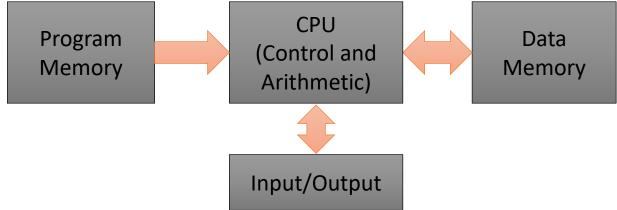

# Hardware Models (1940's)

Harvard Archite

Progr Mem

Von Neumann /

Memory

## Hardware Models (1940's)

Harvard Architecture:

• Von Neumann Architecture:

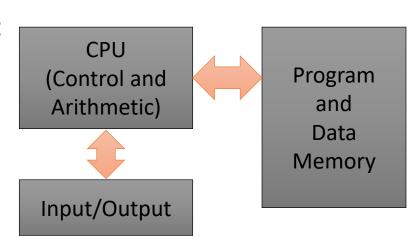

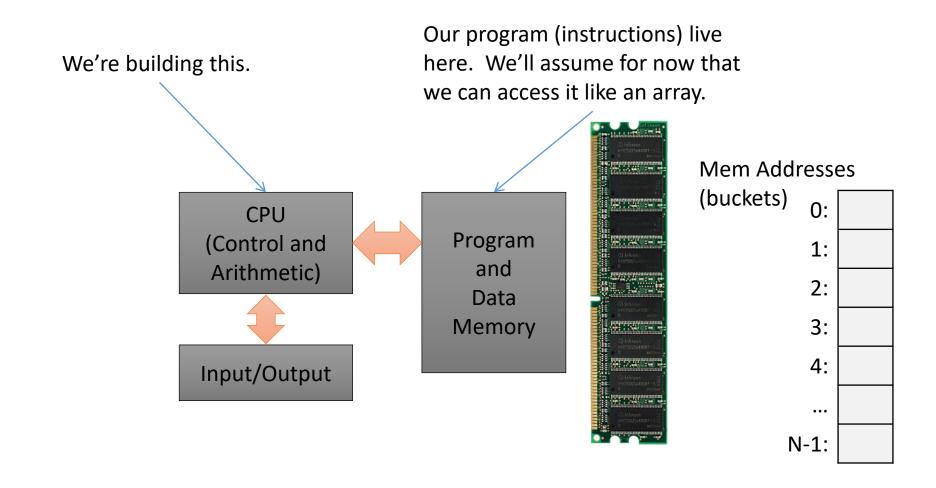

#### Von Neumann Architecture Model

- Computer is a generic computing machine:

- Based on Alan Turing's Universal Turing Machine

- Stored program model: computer stores program rather than encoding it (feed in data and instructions)

- No distinction between data and instructions memory

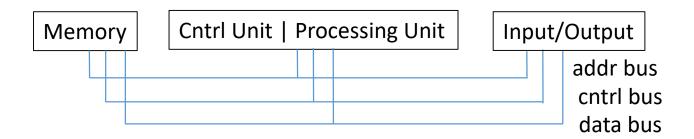

- 5 parts connected by buses (wires):

- Memory, Control, Processing, Input, Output

#### Goal: Build a CPU (model)

#### Three main classifications of HW circuits:

- 1. ALU: implement arithmetic & logic functionality (ex) adder to add two values together

- Storage: to store binary values

(ex) Register File: set of CPU registers, Also: main memory (RAM)

- 3. Control: support/coordinate instruction execution (ex) fetch the next instruction to execute

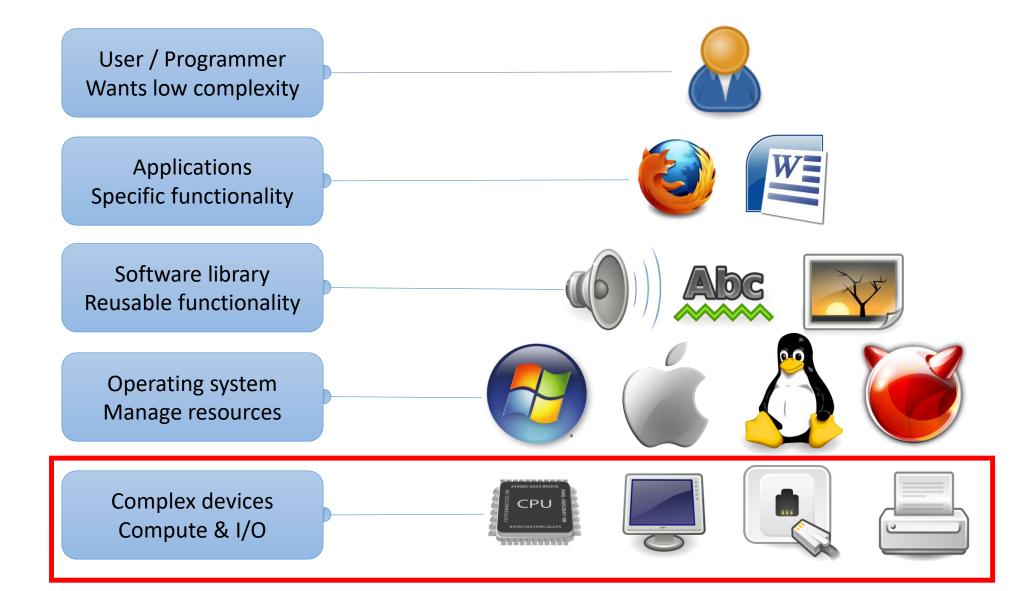

#### Abstraction

#### Abstraction

#### Logic Gates

Input: Boolean value(s) (high and low voltages for 1 and 0)

Output: Boolean value result of Boolean function

Always present, but may change when input changes

| And       |            | 0             | r            | Not                                |  |

|-----------|------------|---------------|--------------|------------------------------------|--|

| a — b — o | ut = a & b | out a b out = | out<br>a   b | a $\rightarrow$ out out = $\sim$ a |  |

| Α         | В          | A & B         | A   B        | ~A                                 |  |

| 0         | 0          | 0             | 0            | 1                                  |  |

| 0         | 1          | 0             | 1            | 1                                  |  |

| 1         | 0          | 0             | 1            | 0                                  |  |

| 1         | 1          | 1             | 1            | 0                                  |  |

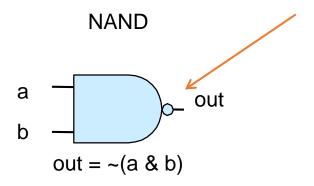

#### More Logic Gates

Note the circle on the output.

This means "negate it."

| _A | В | A NAND B | A NOR B |

|----|---|----------|---------|

| 0  | 0 | 1        | 1       |

| 0  | 1 | 1        | 0       |

| 1  | 0 | 1        | 0       |

| 1  | 1 | 0        | 0       |

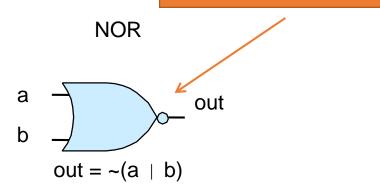

#### Combinational Logic Circuits

Build up higher level processor functionality from basic gates

Outputs are boolean functions of inputs

Outputs continuously respond to changes to inputs

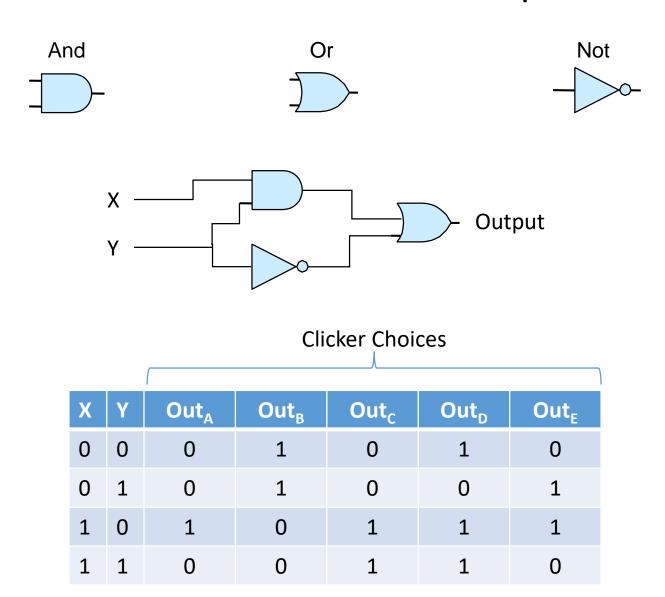

# What does this circuit output?

#### What can we do with these?

Build-up XOR from basic gates (AND, OR, NOT)

| Α | В | A ^ B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 0     |

Q: When is A^B ==1?

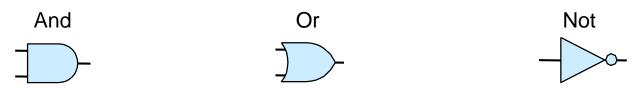

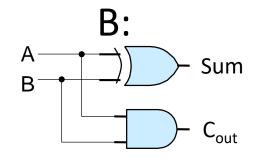

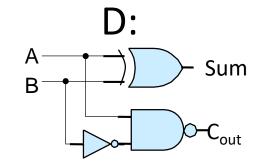

#### Which of these is an XOR circuit?

Draw an XOR circuit using AND, OR, and NOT gates.

I'll show you the clicker options after you've had some time.

#### Which of these is an XOR circuit?

E: None of these are XOR.

#### XOR Circuit: Abstraction

$$A^B == (^A & B) | (A & ^B)$$

A:0 B:0 A^B:

A:0 B:1 A^B:

A:1 B:0 A^B:

A:1 B:1 A^B:

## Digital Circuits - Building a CPU

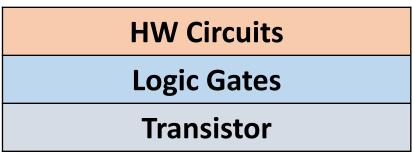

#### Three main classifications of HW circuits:

- 1. ALU: implement arithmetic & logic functionality (ex) adder to add two values together

- 2. Storage: to store binary values (ex) Register File: set of CPU registers

- 3. Control: support/coordinate instruction execution (ex) fetch the next instruction to execute

HW Circuits

Logic Gates

Transistor

#### Digital Circuits - Building a CPU

#### Three main classifications of HW circuits:

1. ALU: implement arithmetic & logic functionality (ex) adder to add two values together

Start with ALU components (e.g., adder)

Combine into ALU!

HW Circuits

Logic Gates

Transistor

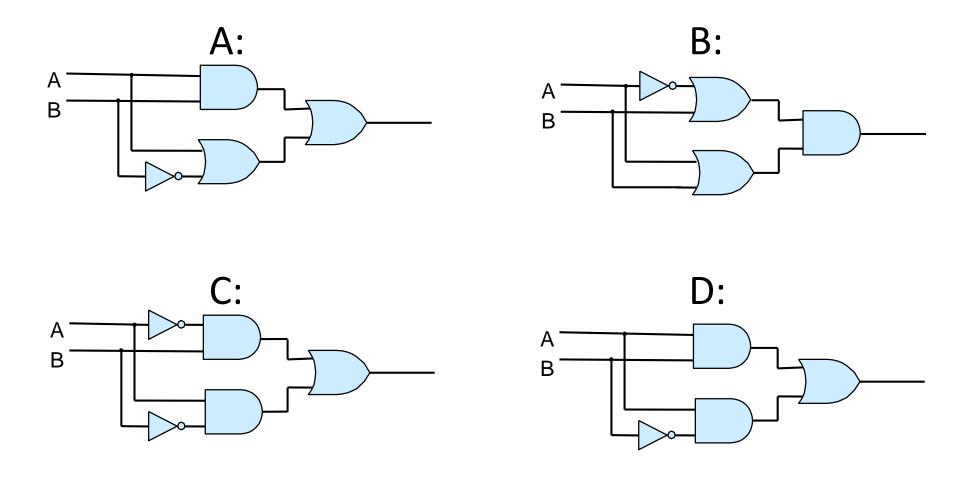

#### **Arithmetic Circuits**

- 1 bit adder: A+B

- Two outputs:

- 1. Obvious one: the sum

- 2. Other one: ??

| Α | В | Sum (A + B) | $C_out$ |

|---|---|-------------|---------|

| 0 | 0 |             |         |

| 0 | 1 |             |         |

| 1 | 0 |             |         |

| 1 | 1 |             |         |

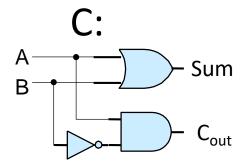

#### Which of these circuits is a one-bit adder?

| Α | В | Sum (A + B) | $C_out$ |

|---|---|-------------|---------|

| 0 | 0 | 0           | 0       |

| 0 | 1 | 1           | 0       |

| 1 | 0 | 1           | 0       |

| 1 | 1 | 0           | 1       |

#### More than one bit?

• When adding, sometimes have carry in too

```

0011010

+ 0001111

```

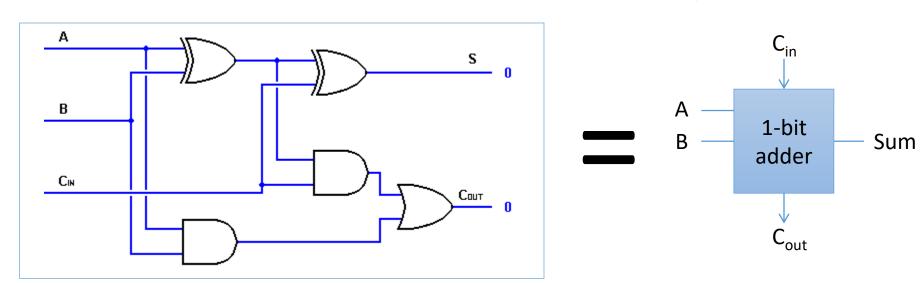

#### One-bit (full) adder

Need to include:

Carry-in & Carry-out

| Α | В | $C_{\mathtt{in}}$ | Sum | $C_out$ |

|---|---|-------------------|-----|---------|

| 0 | 0 | 0                 | 0   | 0       |

| 0 | 1 | 0                 | 1   | 0       |

| 1 | 0 | 0                 | 1   | 0       |

| 1 | 1 | 0                 | 0   | 1       |

| 0 | 0 | 1                 | 1   | 0       |

| 0 | 1 | 1                 | 0   | 1       |

| 1 | 0 | 1                 | 0   | 1       |

| 1 | 1 | 1                 | 1   | 1       |

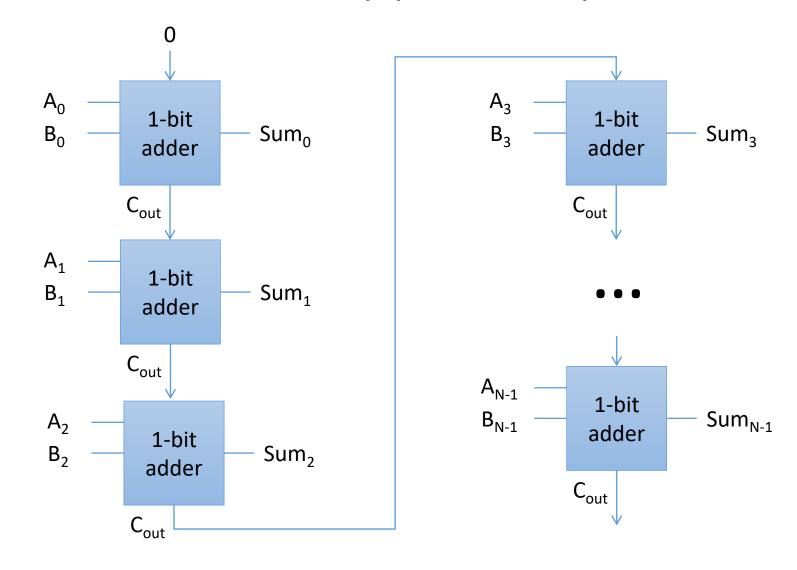

# Multi-bit Adder (Ripple-carry Adder)

# Three-bit Adder (Ripple-carry Adder)

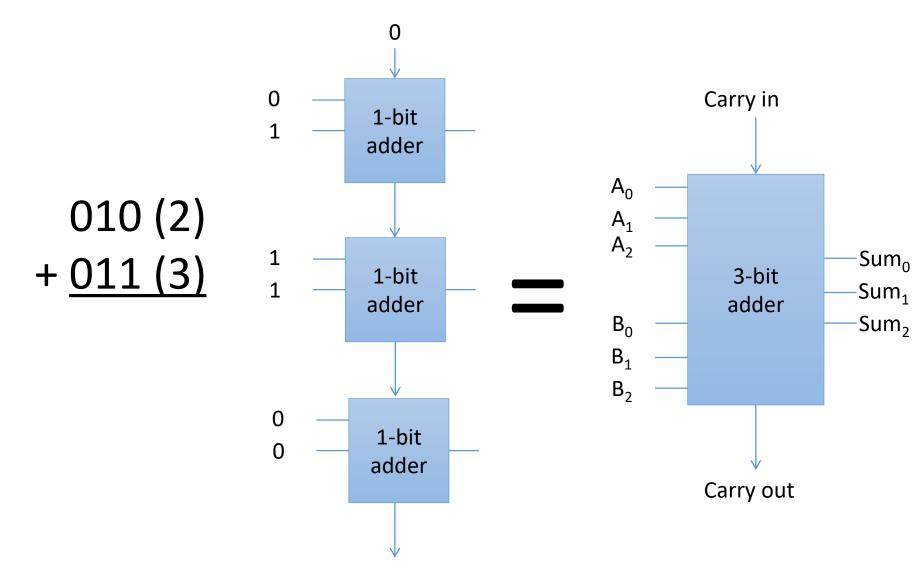

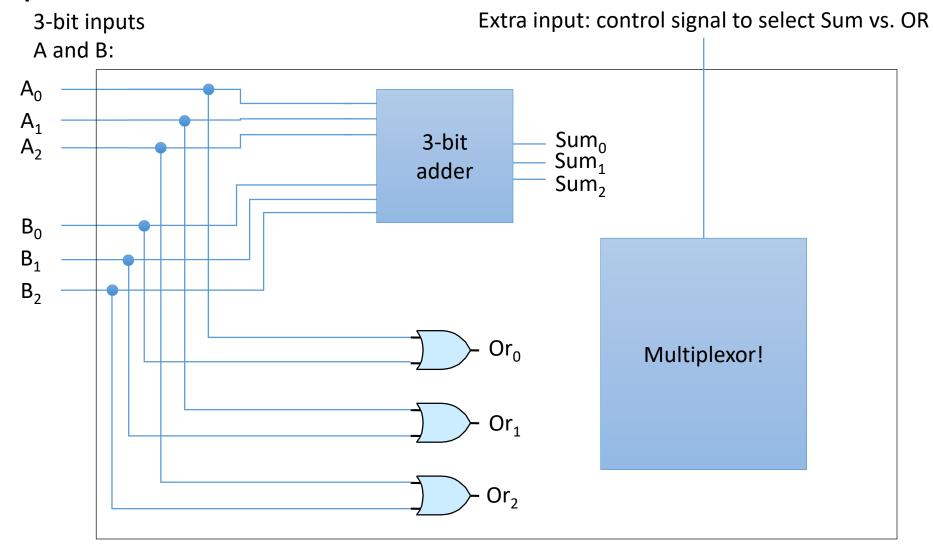

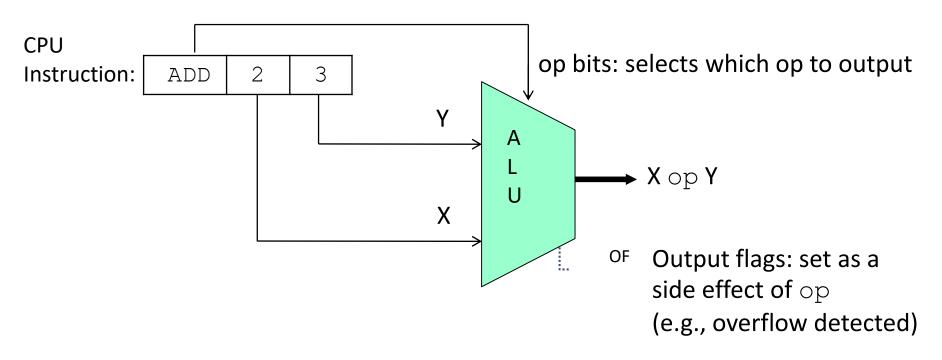

# Arithmetic Logic Unit (ALU)

- One component that knows how to manipulate bits in multiple ways

- Addition

- Subtraction

- Multiplication / Division

- Bitwise AND, OR, NOT, etc.

- Built by combining components

- Take advantage of sharing HW when possible (e.g., subtraction using adder)

3-bit inputs A and B:  $B_0$ Out<sub>o</sub>  $B_2$ -Out₁ Out<sub>2</sub>

3-bit inputs A and B:  $A_0$  $A_1$  $Sum_0$ 3-bit  $A_2$ Sum<sub>1</sub> adder Sum<sub>2</sub>  $B_0$  $B_1$ At any given time, we Out<sub>0</sub>  $B_2$ only want the output -Out₁ Out<sub>2</sub> from ONE of these!  $Or_0$  $Or_1$  $Or_2$

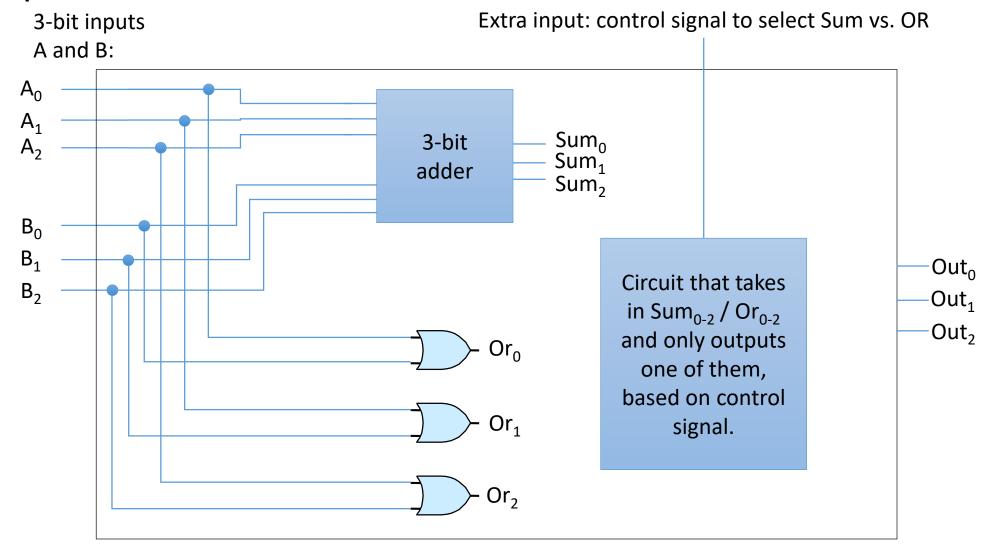

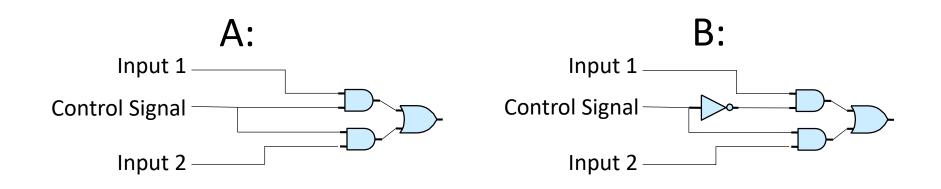

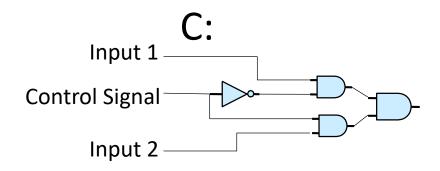

# Which of these circuits lets us select between two inputs?

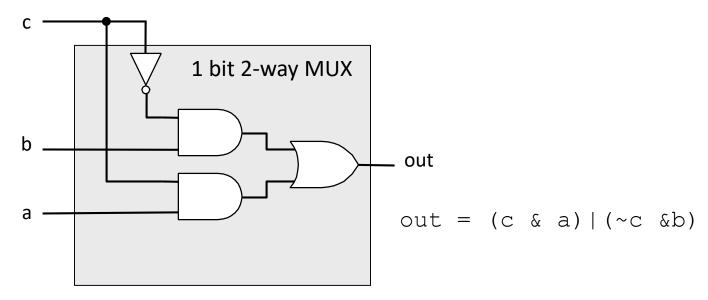

### Multiplexor: Chooses an input value

<u>Inputs</u>: 2<sup>N</sup> data inputs, N signal bits

Output: is one of the 2<sup>N</sup> input values

- Control signal c, chooses the input for output

- When c is 1: choose a, when c is 0: choose b

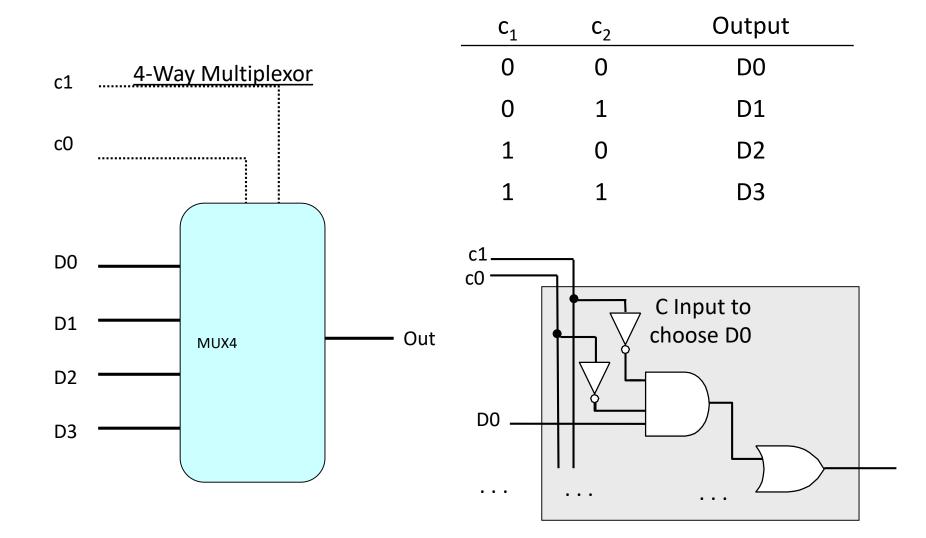

# N-Way Multiplexor

Choose one of N inputs, need log<sub>2</sub> N select bits

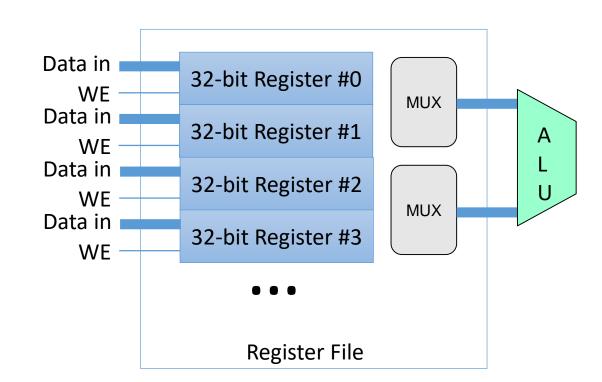

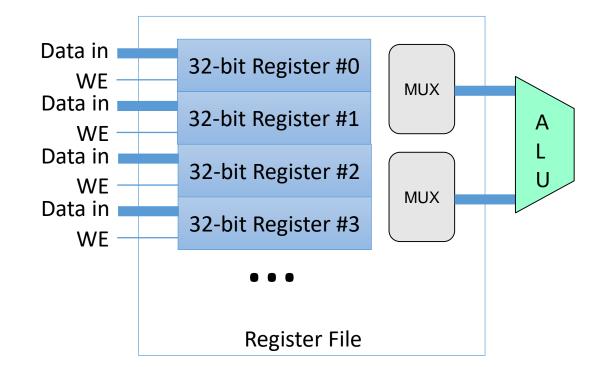

#### ALU: Arithmetic Logic Unit

- Arithmetic and logic circuits: ADD, SUB, NOT, ...

- Control circuits: use op bits to select output

- Circuits around ALU:

- Select input values X and Y from instruction or register

- Select op bits from instruction to feed into ALU

- Feed output somewhere

## Digital Circuits - Building a CPU

#### Three main classifications of HW circuits:

- 1. ALU: implement arithmetic & logic functionality (ex) adder to add two values together

- 2. Storage: to store binary values (ex) Register File: set of CPU registers

- 3. Control: support/coordinate instruction execution (ex) fetch the next instruction to execute

Circuits are built from Logic Gates which are built from transistors

#### Digital Circuits - Building a CPU

#### Three main classifications of HW circuits:

2. Storage: to store binary values

(ex) Register File: set of CPU registers

Give the CPU a "scratch space" to perform calculations and keep track of the state its in.

HW Circuits

Logic Gates

Transistor

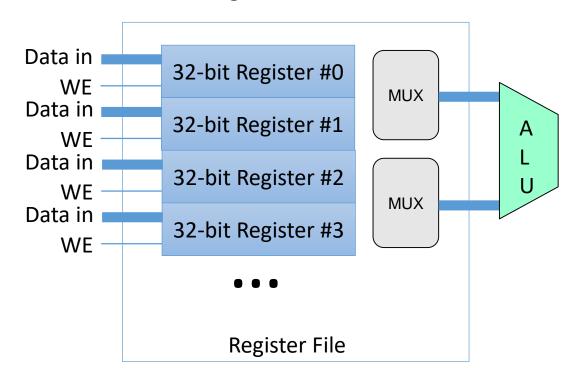

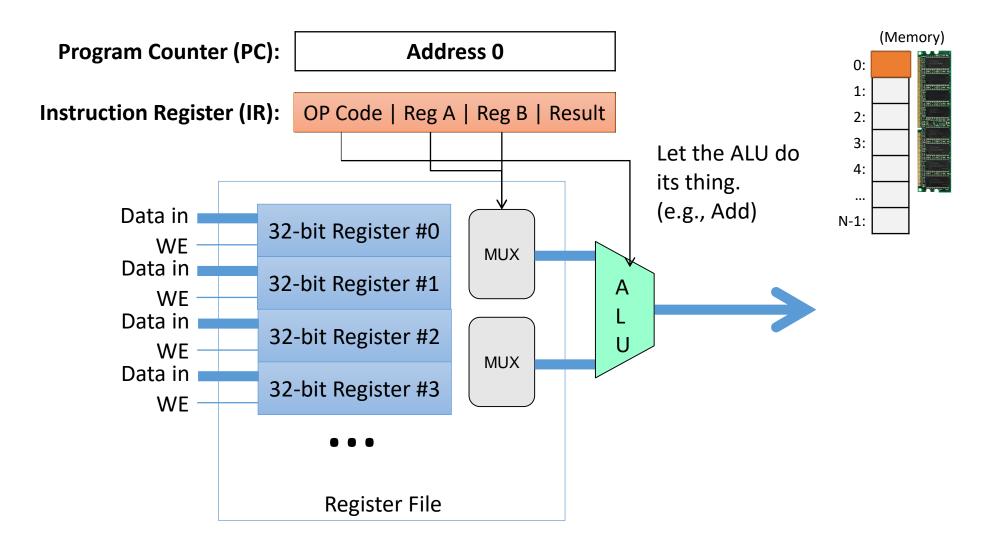

### CPU so far...

- We can perform arithmetic!

- Storage questions:

- Where to the ALU input values come from?

- Where do we store the result?

- What does this "register" thing mean?

## Memory Circuit Goals: Starting Small

• Store a 0 or 1

Retrieve the 0 or 1 value on demand (read)

Set the 0 or 1 value on demand (write)

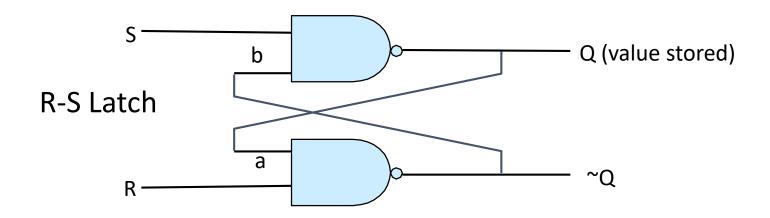

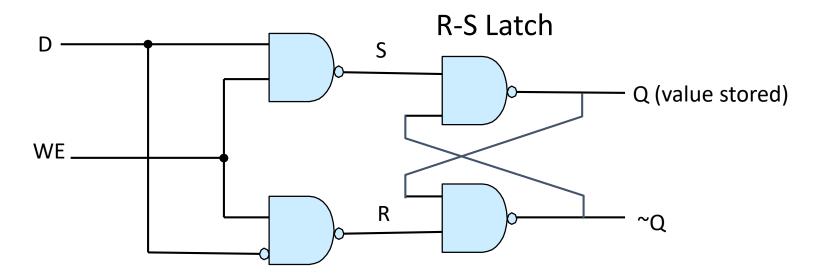

### R-S Latch: Stores Value Q

When R and S are both 1: Maintain a value R and S are never both simultaneously 0

- To write a new value:

- Set S to 0 momentarily (R stays at 1): to write a 1

- Set R to 0 momentarily (S stays at 1): to write a 0

### Gated D Latch

Controls S-R latch writing, ensures S & R never both 0

D: into top NAND, ~D into bottom NAND

WE: write-enabled, when set, latch is set to value of D

Latches used in registers (up next) and SRAM (caches, later) Fast, not very dense, expensive

DRAM: capacitor-based:

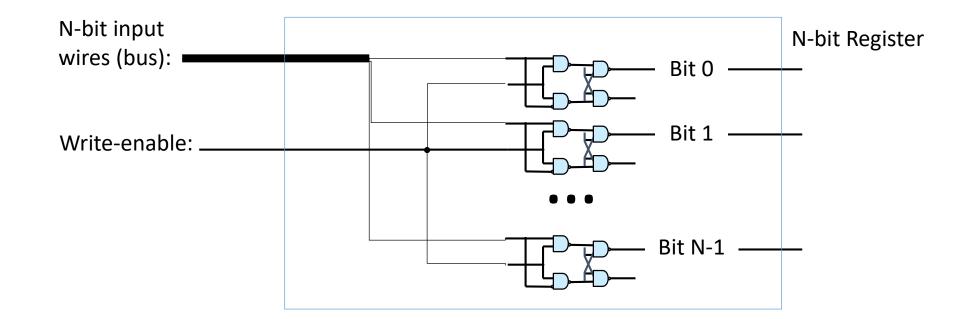

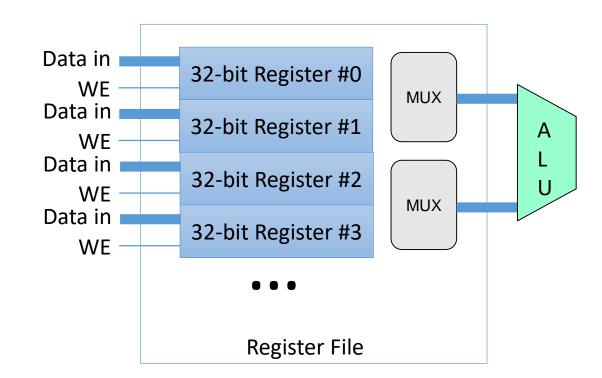

## Registers

- Fixed-size storage (8-bit, 32-bit, etc.)

- Gated D latch lets us store one bit

- Connect N of them to the same write-enable wire!

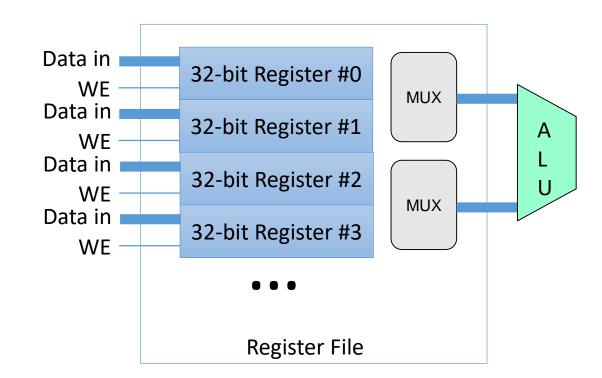

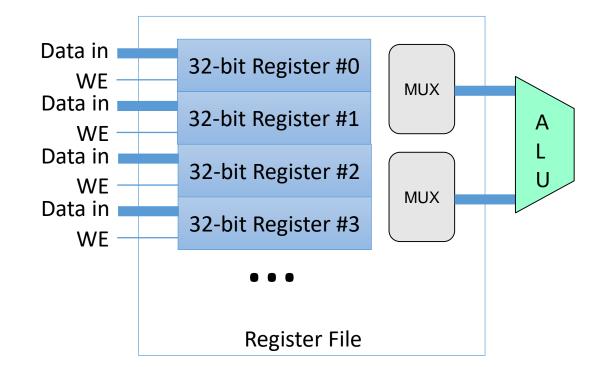

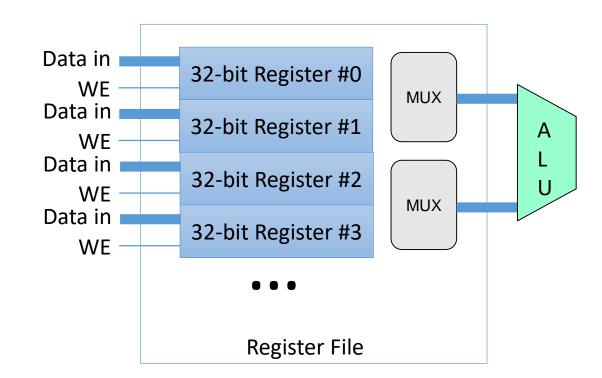

## "Register file"

• A set of registers for the CPU to store temporary values.

This is (finally) something you will interact with!

• Instructions of form:

• "add R1 + R2, store result in R3"

## Memory Circuit Summary

- Lots of abstraction going on here!

- Gates hide the details of transistors.

- Build R-S Latches out of gates to store one bit.

- Combining multiple latches gives us N-bit register.

- Grouping N-bit registers gives us register file.

- Register file's simple interface:

- Read R<sub>x</sub>'s value, use for calculation

- Write R<sub>v</sub>'s value to store result

## Digital Circuits - Building a CPU

### Three main classifications of HW circuits:

- 1. ALU: implement arithmetic & logic functionality (ex) adder to add two values together

- 2. Storage: to store binary values (ex) Register File: set of CPU registers

- 3. Control: support/coordinate instruction execution (ex) fetch the next instruction to execute

Circuits are built from Logic Gates which are built from transistors

## Digital Circuits - Building a CPU

#### Three main classifications of HW circuits:

3. Control: support/coordinate instruction execution (ex) fetch the next instruction to execute

Keep track of where we are in the program.

Execute instruction, move to next.

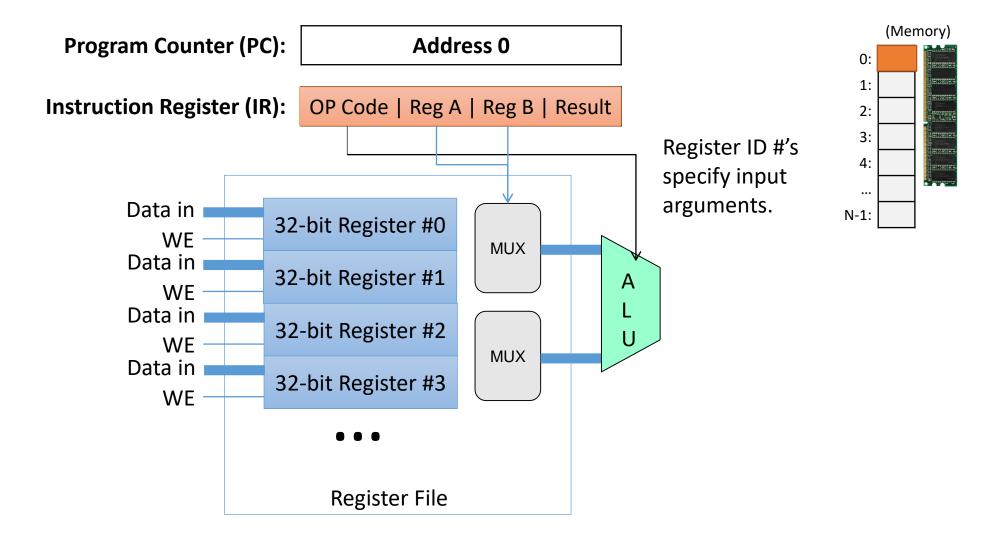

### CPU so far...

We know how to store data (in register file).

We know how to perform arithmetic on it, by feeding it to ALU.

#### Remaining questions:

Which register(s) do we use as input to ALU? Which operation should the ALU perform? To which register should we store the result?

All this info comes from our program: a series of instructions.

### Recall: Von Neumann Model

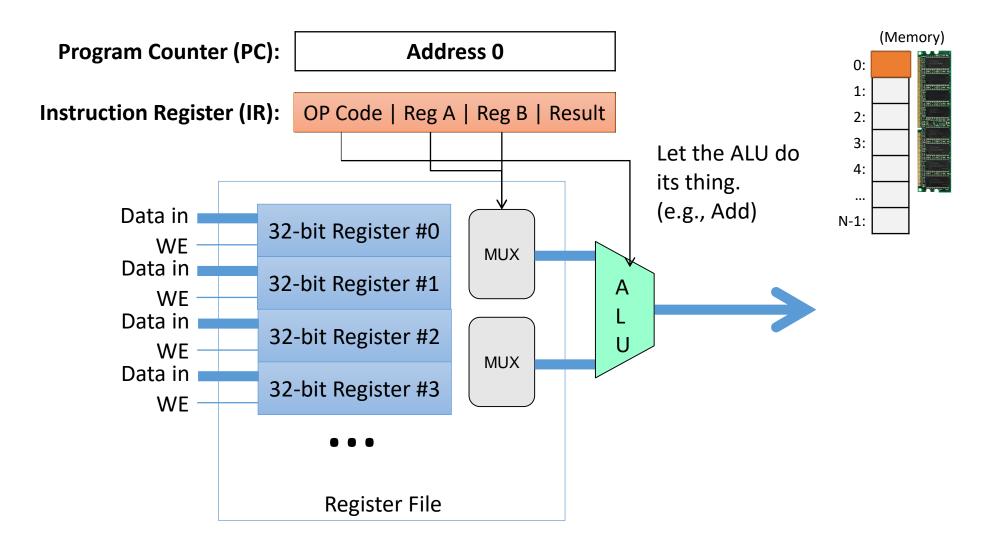

### CPU Game Plan

Fetch instruction from memory

- Decode what the instruction is telling us to do

- Tell the ALU what it should be doing

- Find the correct operands

- Execute the instruction (arithmetic, etc.)

- Store the result

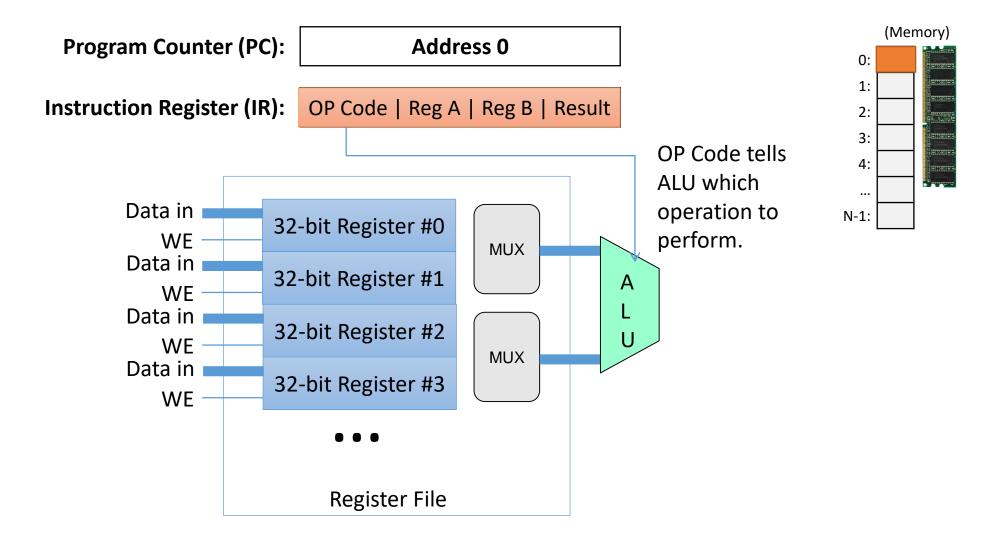

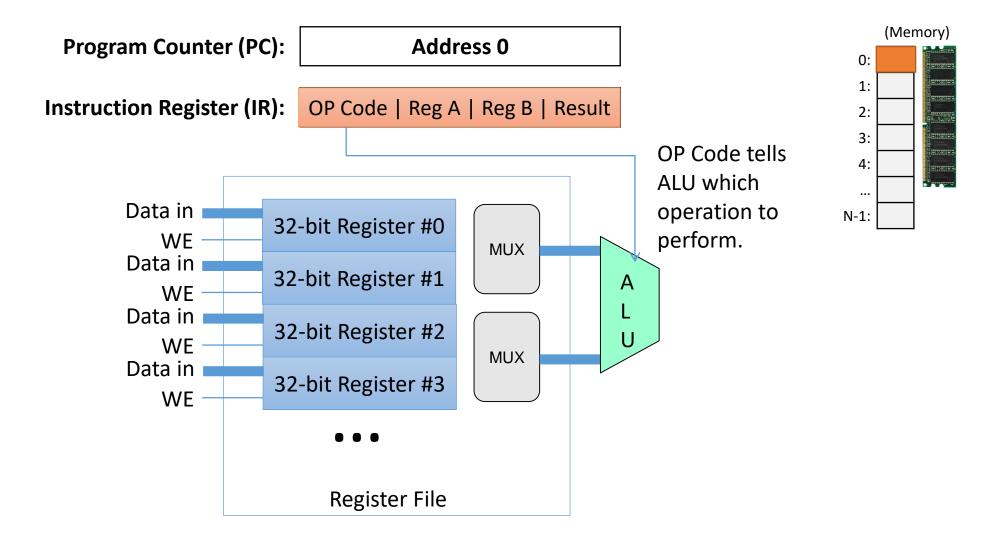

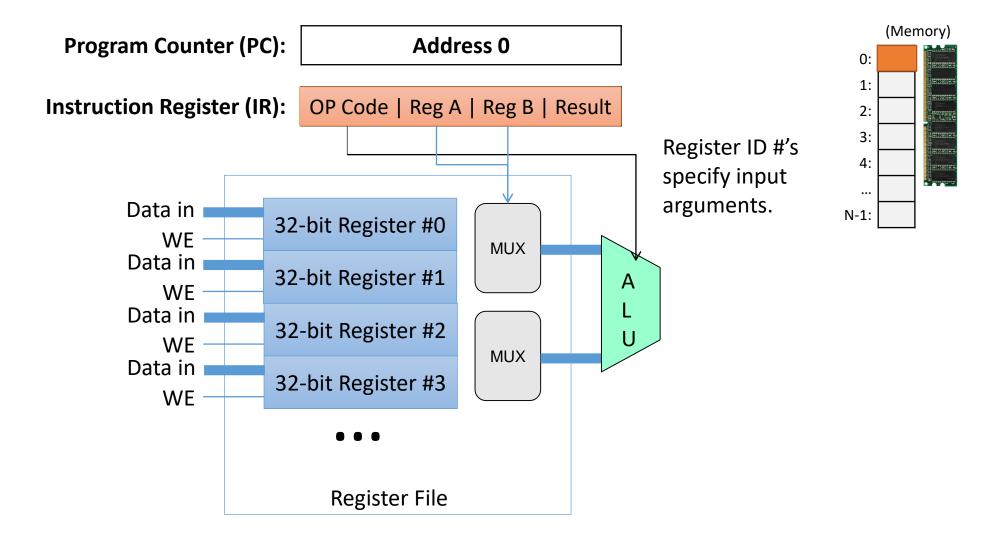

## Program State

Let's add two more special registers (not in register file) to keep track of program.

Program Counter (PC): Memory address of next instr

Instruction Register (IR): In

**Instruction contents (bits)**

## Fetching instructions.

Load IR with the contents of memory at the address stored in the PC.

Program Counter (PC): Address 0

Instruction Register (IR): Instruction at Address 0

Interpret the instruction bits: What operation? Which arguments?

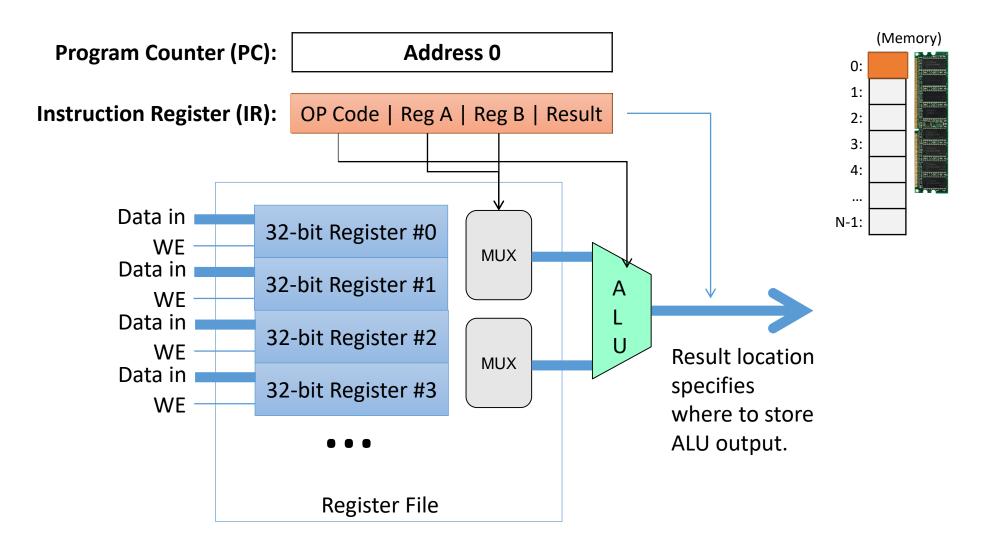

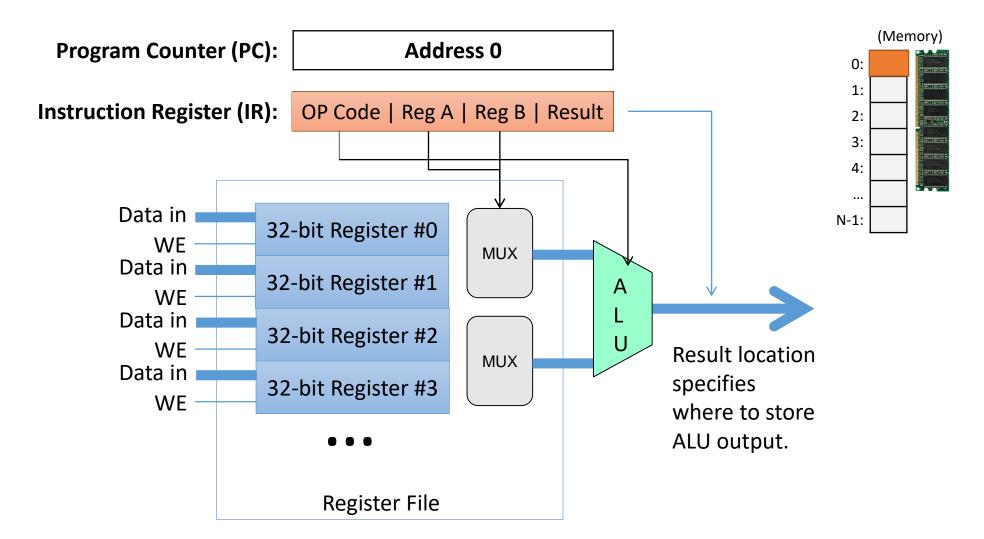

Program Counter (PC): Address 0

Instruction Register (IR): OP Code | Reg A | Reg B | Result

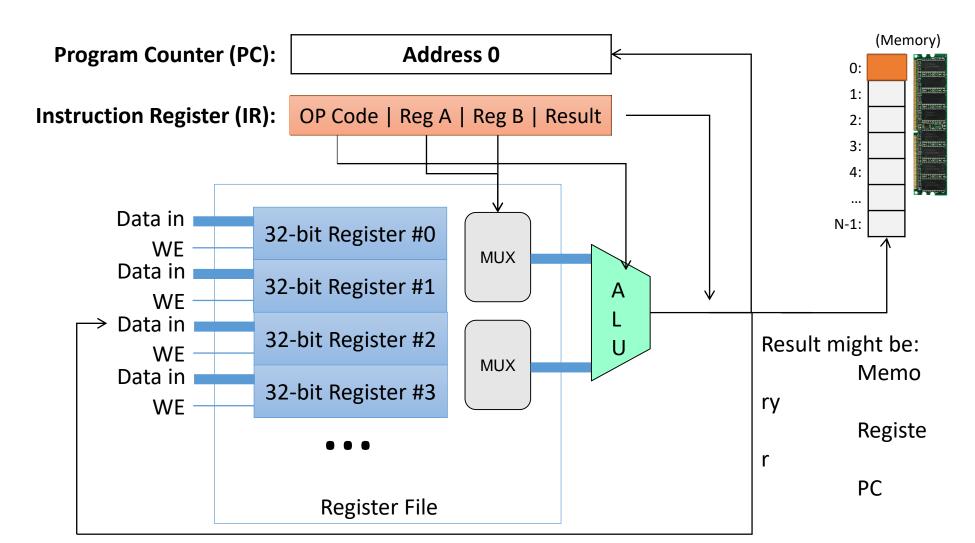

## Executing instructions.

## Storing results.

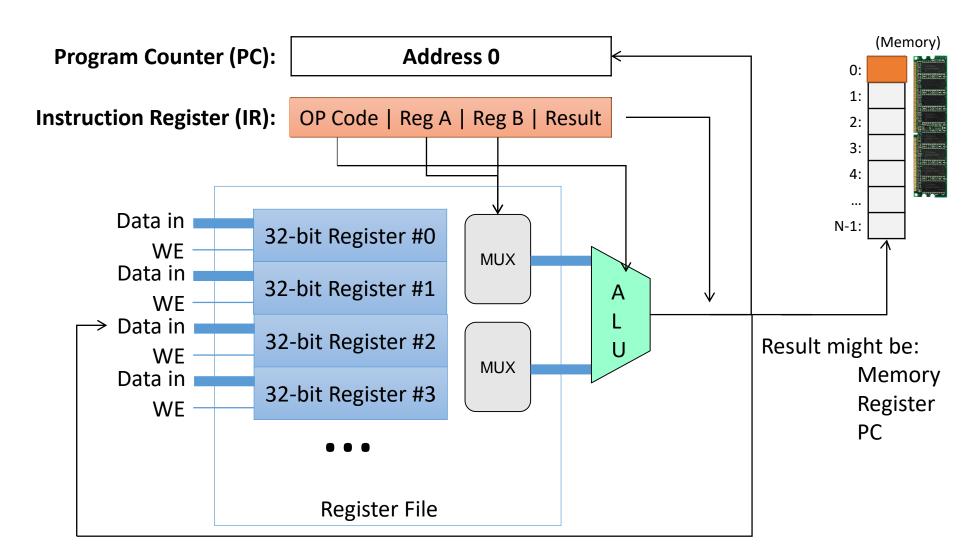

We've just computed something. Where do we put it?

## Questions so far?

We've just computed something. Where do we put it?

Why do we need a program counter? Can't we just start executing instruction at address 0 and count up one at a time from there?

- A. We don't, it's there for convenience.

- B. Some instructions might skip the PC forward by more than one.

- C. Some instructions might adjust the PC backwards.

- D. We need the PC for some other reason(s).

## Storing results.

## Recap CPU Model

Four stages: fetch instruction, decode instruction, execute, store result

Program Counter (PC): | Memory address of next instr

Instruction Register (IR): Instruction contents (bits)

## Fetching instructions.

Load IR with the contents of memory at the address stored in the PC.

Program Counter (PC): Address 0

Instruction Register (IR): Instruction at Address 0

Interpret the instruction bits: What operation? Which arguments?

Program Counter (PC): Address 0

Instruction Register (IR): OP Code | Reg A | Reg B | Result

## Executing instructions.

## Storing results.

Interpret the instruction bits: Store result in register, memory, PC.

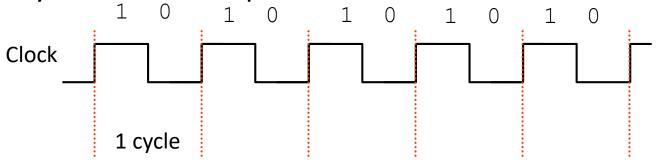

## Clocking

• Need to periodically transition from one instruction to the next.

- It takes time to fetch from memory, for signal to propagate through wires, etc.

- Too fast: don't fully compute result

- Too slow: waste time

## Clock Driven System

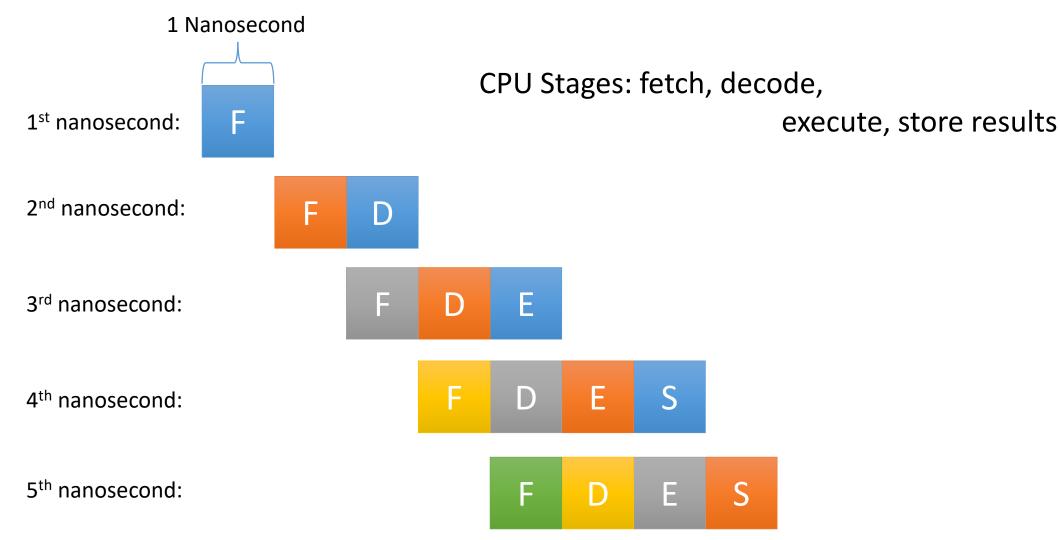

- Everything in a CPU is driven by a discrete clock

- clock: an oscillator circuit, generates hi low pulse

- clock cycle: one hi-low pair

- Clock determines how fast system runs

- Processor can only do one thing per clock cycle

- Usually just one part of executing an instruction

- 1GHz processor:

1 billion cycles/second → 1 cycle every nanosecond

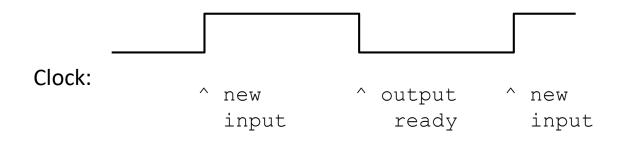

### Clock and Circuits

### **Clock Edges Triggers events**

- Circuits have continuous values

- Rising Edge: trigger new input values

- Falling Edge: consistent output ready to read

- Between rising and falling edge can have inconsistent state as new input values flow through circuit

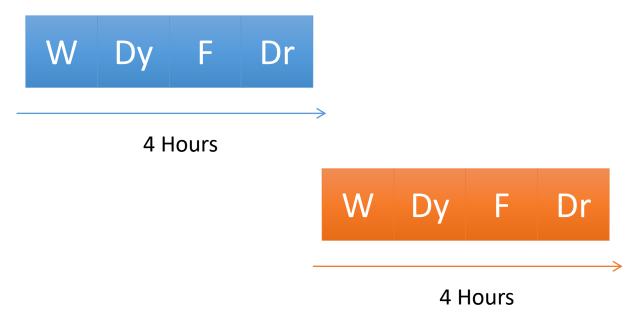

## Cycle Time: Laundry Analogy

• Discrete stages: fetch, decode, execute, store

• Analogy (laundry): washer, dryer, folding, dresser

You have big problems if you have millions of loads of laundry to do....

## Laundry

4-hour cycle time.

Finishes a laundry load every cycle.

(6 laundry loads per day)

4 Hours

## Pipelining (Laundry)

Steady state: One load finishes every hour! (Not every four hours like before.)

# Pipelining (CPU)

Steady state: One instruction finishes every nanosecond! (Clock rate can be faster.)

## Pipelining

(For more details about this and the other things we talked about here, take architecture.)

## Up next

• Talking to the CPU: Assembly language