## CS31 Worksheet: Week 9: Caching

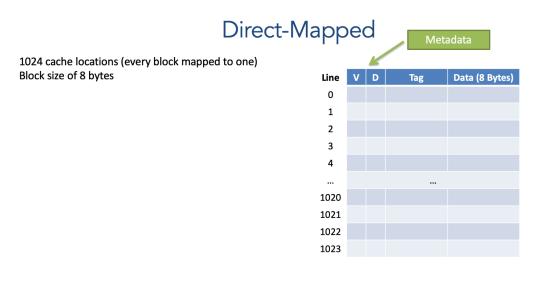

## Address division: Direct-Mapped

## Direct-Mapped Example

VD Tag Data Line • Let's say we access memory at (16 Bytes) address: 0 - 01101011 0011 0100 1 2 • Step 2: 3 - Use index to find line (row) 4 - 0011 -> 3 5 .... 15

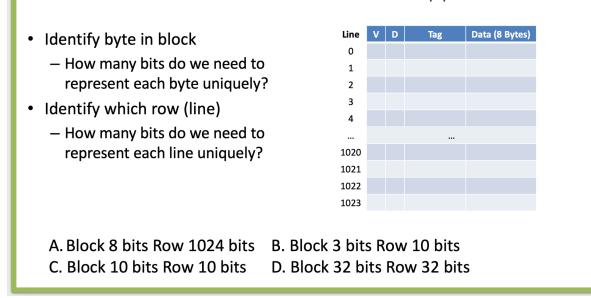

Suppose we had 8-bit addresses, a cache with 8 lines, and a block size of 4 bytes.

- How many bits would we use for:

- Tag?

- Index?

- Offset?

## Memory address

Read 01000100 (Value: 5) Read 11100010 (Value: 17) Write 01110000 (Value: 7) Read 10101010 (Value: 12) Write 01101100 (Value: 2)

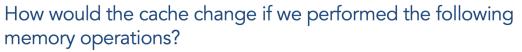

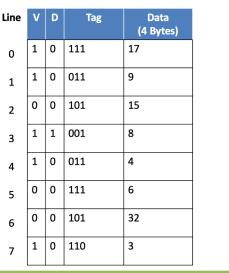

How would the cache change if we performed the following memory operations? (2-way set)

Read 01000100 (Value: 5) Read 11100010 (Value: 17) Write 01100100 (Value: 7) Read 01000110 (Value: 5) Write 01100000 (Value: 2)

LRU = 0 means: the left line in the set was least recently used. LRU = 1 means: the right line in the set was least recently used.

|  | Set # | LRU | v | D | Tag | Data (4 Bytes) | V | D | Tag | Data (4 Bytes) |

|--|-------|-----|---|---|-----|----------------|---|---|-----|----------------|

|  | 0     | 1   | 0 | 0 | 111 | 4              | 1 | 0 | 001 | 17             |

|  | 1     | 0   | 1 | 1 | 111 | 9              | 1 | 0 | 010 | 5              |

|  | 2     |     |   |   |     |                |   |   |     |                |

|  | 3     |     |   |   |     |                |   |   |     |                |

|  | 4     |     |   |   |     |                |   |   |     |                |

|  | 5     |     |   |   |     |                |   |   |     |                |

|  | 6     |     |   |   |     |                |   |   |     |                |

|  | 7     |     |   |   |     |                |   |   |     |                |